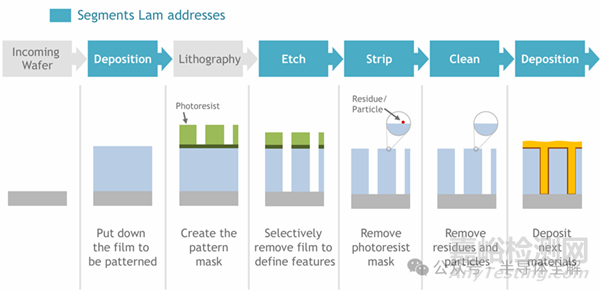

在芯片的生產(chǎn)過程中���,主要有八大工序��,其中光刻與刻蝕是兩大核心工序���。常見的芯片生產(chǎn)過程如下圖所示:

芯片制造過程主要用到的設(shè)備如下圖:

這一節(jié)將簡單介紹刻蝕技術(shù),刻蝕可分為干法刻蝕和濕法刻蝕���,這兩種刻蝕方法各有優(yōu)缺點(diǎn)���。隨著芯片制程走向高端,干法刻蝕的使用越來越廣泛��,干法刻蝕又可以細(xì)分成不同的設(shè)備�����。

常見的干法刻蝕設(shè)備有感應(yīng)耦合等離子體(Inductively Coupled Plasma,ICP)刻蝕機(jī)?反應(yīng)離子(Reactive Ion Etching,RIE)刻蝕機(jī)和離子束刻蝕機(jī)(Ion Beam Etching,IBE)?

依據(jù)刻蝕氣體和刻蝕原理之間的區(qū)別,將各設(shè)備用于刻蝕不同材料,需要被刻蝕的材料有GaN?Si02?Si3N4和金屬等�����。

二�����、ICP干法刻蝕介紹

ICP刻蝕的基本原理是將ICP射頻電源產(chǎn)生射頻信號輸出到耦合線圈,刻蝕氣體經(jīng)過耦介后輝光放電形成等離子體,在RF射頻單元的作用下,等離子體以一定的能量轟擊到樣品表面,發(fā)生物理和化學(xué)刻蝕作用,刻蝕得到的反應(yīng)產(chǎn)物由真空系統(tǒng)抽走?

在進(jìn)行ICP刻蝕時(shí),需提供的刻蝕氣體有BCl3?Cl2?Ar?02?N2和CH4?

刻蝕GaN基材料常用含Cl的BCl3��、Cl2氣體,以增大化學(xué)刻蝕比例,從而減小物理轟擊對GaN基材料的刻蝕損傷?

RIE刻蝕設(shè)備提供的刻蝕氣體有SF6?CHF3?O2和He,通常用RIE刻蝕SiO2和Si3N4薄膜,其基本反應(yīng)原理是利用在射頻作用下產(chǎn)生F基等離子體對材料產(chǎn)生物理和化學(xué)刻蝕,主要為化學(xué)刻蝕起作用通常用IBE刻蝕設(shè)備對金屬材料進(jìn)行刻蝕,刻蝕原理是將Ar氣電離形成Ar離子,Ar離子在電場下加速轟擊樣品表面,使原子脫落并被抽走?

IBE刻蝕是純物理刻蝕過程,具備較好的各向異性,但是刻蝕速率較慢?

三��、反應(yīng)離子干法刻蝕介紹

反應(yīng)離子刻蝕(Reactive Ion Etching, RIE)可以將光刻版上的臺面圖形轉(zhuǎn)移到SiO2掩膜上,并使用感應(yīng)耦合等離子體刻蝕(Inductively Coupled Plasma, ICP)來刻蝕形成臺面結(jié)構(gòu),因此對于等離子體刻蝕原理以及這兩種設(shè)備的刻蝕參數(shù)與刻蝕過程進(jìn)行介紹?

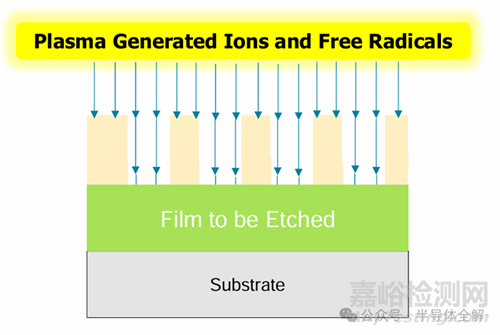

(1)等離子體刻蝕原理

等離子體刻蝕涉及到物理作用及化學(xué)作用?

通過向氣體施加電場后,氣體分子會電離形成的由離子?電子?自由基和中性粒子組成的物質(zhì)狀態(tài),稱為等離子體?

在等離子體狀態(tài)下,氣體分子被激發(fā)并電離,從而產(chǎn)生自由電子和離子,具有獨(dú)特的特性,因此適合于精密刻蝕?

活性粒子中的自由基是一些電中性但化學(xué)活性極強(qiáng)的粒子(如F?cl-),吸附在材料表面,通過化學(xué)鍵的斷裂與重組進(jìn)行化學(xué)反應(yīng),同時(shí)生成揮發(fā)性產(chǎn)物;而等離子體中的離子帶正電,在高能電場的作用下被吸引到帶有負(fù)偏壓的基板表面,并直接轟擊表面原子?

化學(xué)刻蝕具有各項(xiàng)同性的特點(diǎn),選擇性高但方向性差,因此其橫向刻蝕明顯;而物理特性具有各向異性的特點(diǎn),以垂直方向?yàn)橹?方向性好但選擇性低?

因此在進(jìn)行等離子體刻蝕時(shí),通過調(diào)節(jié)工藝參數(shù)(腔壓?ICP及RF功率)以及將各個(gè)氣體調(diào)節(jié)到合適的配比,控制自由基與離子的比例,實(shí)現(xiàn)化學(xué)與物理刻蝕的協(xié)同作用,從而保證刻蝕效果?

(2)刻蝕設(shè)備與刻蝕步驟

在后續(xù)工藝制備步驟中,所使用的RIE主要用于將光刻膠的圖形轉(zhuǎn)移到SiO2上,這是因?yàn)樵谑褂肐CP刻蝕InP?InGaAs?InGaAsP等材料時(shí),常需要高溫刻蝕,此時(shí)的光刻膠會由于高溫而變性,粘附在片子上,必須要采用耐高溫且刻蝕選擇比(刻蝕所需材料速度與刻蝕掩膜速度的比值)高的SiO2作為掩膜?

而ICP則因?yàn)楦叩目涛g速率與各向異性的刻蝕效果,成為刻蝕Ⅲ-Ⅴ族材料的首選?

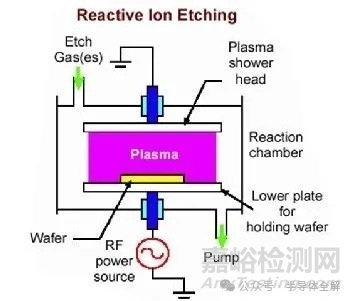

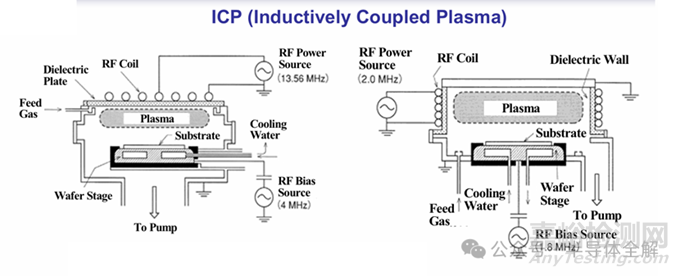

RIE與ICP設(shè)備之間的主要區(qū)別在于設(shè)備結(jié)構(gòu)上,如下圖所示?

RIE設(shè)備中只有一個(gè)放置于刻蝕腔體之下的射頻(RF)電源,用于產(chǎn)生偏置電壓,提供能量使等離子體垂直作用于基片進(jìn)行刻蝕;

而ICP設(shè)備中在腔體之上則還包含一個(gè)ICP射頻源,由環(huán)形線圈組成,通過電感耦合的方式使輸入氣體輝光放電,用于產(chǎn)生高密度的等離子體,進(jìn)而實(shí)現(xiàn)等離子體密度和能量在一定程度上的分離?

四�����、干法刻蝕工藝步驟

(1)RIE的刻蝕參數(shù)與刻蝕步驟

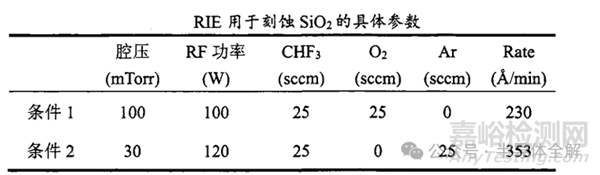

SiO2的刻蝕主要使用CHF3與O2組合或CHF3與Ar組合,具體刻蝕參數(shù)如下表所示?

條件2對于SiO2的刻蝕速率快于條件1,并且與AZ5214E光刻膠的選擇刻蝕比能夠達(dá)到3:1,而條件1僅有1:1?

然而,使用CHF3與Ar的氣體組合對于SiO2刻蝕后,由于化學(xué)刻蝕作用過強(qiáng),會在片子表面生成較多的聚合物,影響后續(xù)工藝的進(jìn)行?因此在光刻膠厚度足夠的情況下,優(yōu)先使用條件1的工藝條件?

使用RIE對于SiO2進(jìn)行刻蝕時(shí),將片子放入反應(yīng)腔室內(nèi)部后,對腔內(nèi)進(jìn)行抽真空操作,避免殘留氣體的污染?隨后運(yùn)行刻蝕程序,首先按比例通入刻蝕氣體和輔助氣體,然后啟動(dòng)射頻電源,氣體將電離形成等離子體?

(2)ICP的刻蝕參數(shù)與刻蝕步驟

ICP對于光電探測器中的InP?InGaAs?InGaAsP材料進(jìn)行刻蝕時(shí),常采用高溫刻蝕程序,通常使用含氯元素的氣體來進(jìn)行刻蝕?

通常使用以SiCl4為主的刻蝕氣體,而由于在化學(xué)刻蝕時(shí),常會產(chǎn)生難揮發(fā)的氣體聚合物InClx,沉積在表面會影響進(jìn)一步的刻蝕及工藝步驟,因此還通入一定氣流量的N2?Ar等惰性氣體,增加腔內(nèi)的離子密度,從而增強(qiáng)物理作用,減少氣體聚合物的生成與沉積?

具體使用的工藝條件如下:

(3)刻蝕步驟:

在Si02掩膜制作完成后,對片子進(jìn)行預(yù)處理:在片子背面涂抹栗油,從而增強(qiáng)散熱,但需要注意控制用量?隨后將片子放置在4寸的圓形硅片上,放置進(jìn)入Load Lock預(yù)抽真空室?在Load lock腔內(nèi)預(yù)抽真空,隨后基片傳送入反應(yīng)腔室,被壓板壓住,反應(yīng)腔室進(jìn)行進(jìn)一步的抽真空操作�����,通入一定量的工藝氣體,并等待氣流量穩(wěn)定?

通入氦氣用于散熱,等待其氣流量穩(wěn)定?射頻功率穩(wěn)定且反向射頻功率降至0,各項(xiàng)指標(biāo)達(dá)到容許值范圍內(nèi)后,氣體在射頻功率的作用下起輝產(chǎn)生等離子體,按照設(shè)定的時(shí)間進(jìn)行刻蝕程序?

刻蝕程序完成后,反應(yīng)腔室內(nèi)仍然進(jìn)行多次的抽真空操作,用于盡可能將反應(yīng)生成的氣體排入尾氣處理裝置,隨后基片從反應(yīng)腔室中被傳送入Load lock腔內(nèi)?待Load lock腔進(jìn)行多次的充氣?抽真空操作后,其內(nèi)氣壓升至大氣壓,我們即可打開Load lock腔,取出片子?

一般來說,在刻蝕時(shí),首先以陪片刻蝕速率為參考,進(jìn)行正式片的第一步刻蝕約刻到這一步所需臺面高度的80%,進(jìn)行臺階高度測量,計(jì)算出探測器材料與掩膜的刻蝕選擇比,再進(jìn)行第二步刻蝕,需要確?����?涛g冗余高度在10%以內(nèi)?

好了���,關(guān)于芯片刻蝕工藝就介紹到這兒,對半導(dǎo)體感興趣的同學(xué)歡迎關(guān)注《半導(dǎo)體全解》���,一起了解更多半導(dǎo)體知識���!

參考文獻(xiàn):

(1)董曉雯 光載無線系統(tǒng)中高速高飽和光電探測器及光互連收發(fā)一體芯片研究[D].

(2)閆書萌 NPN型GaN異質(zhì)結(jié)雙極型晶體管的研究[D].

(3)楊鵬 雙層堆疊的三維相變存儲器刻蝕工藝研究[D].

(4)雷雨璋 先進(jìn)等離子體干法刻蝕工藝形貌效應(yīng)仿真與驗(yàn)證研究[D].

(5)宋昊宇 基于CF_4等離子體二維流體模型的ICP刻蝕設(shè)備結(jié)構(gòu)優(yōu)化與工藝參數(shù)分析[D].