概述2026

近年來���,芯粒設(shè)計(jì)與異質(zhì)集成封裝技術(shù)受到了行業(yè)內(nèi)的廣泛關(guān)注�����,F(xiàn)PGA(如賽靈思與臺(tái)積電合作的Virtex系列)�����、微處理器(如AMD的EPYC系列、英特爾的Lakefield系列)等產(chǎn)品�,均借助芯粒設(shè)計(jì)與異質(zhì)集成技術(shù)實(shí)現(xiàn)了大規(guī)模量產(chǎn)。本文將對(duì)這兩項(xiàng)技術(shù)進(jìn)行詳細(xì)介紹����,首先明確片上系統(tǒng)(SoC)����、芯粒設(shè)計(jì)及異質(zhì)集成 封裝的定義�����,并分析其各自的優(yōu)勢與劣勢���。

片上系統(tǒng)(SoC)2026

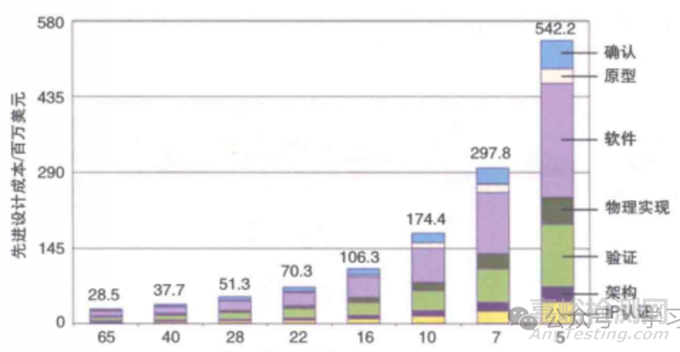

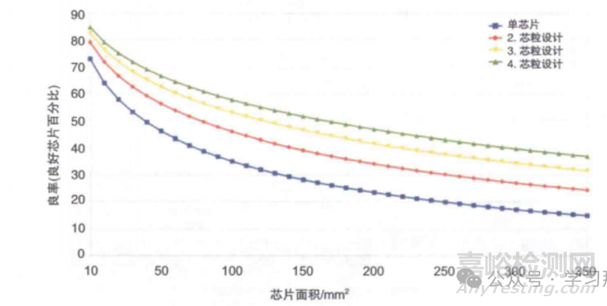

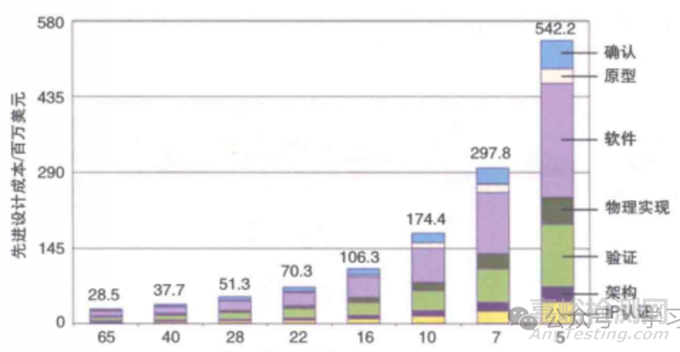

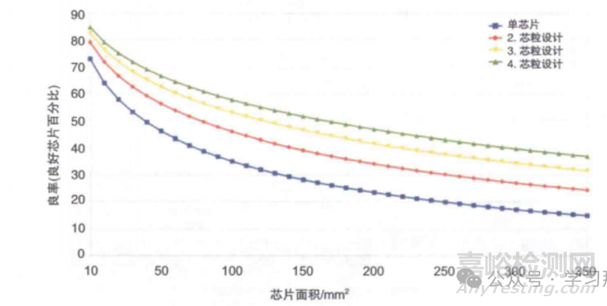

片上系統(tǒng)(SoC)是將多種具備不同功能的集成電路�����,包括中央處理器(CPU)、圖形處理器(GPU)���、存儲(chǔ)器等,集成到單一芯片之中,進(jìn)而構(gòu)成一個(gè)完整的系統(tǒng)或子系統(tǒng)����。目前業(yè)界最具代表性的SoC產(chǎn)品是蘋果公司的應(yīng)用處理器(AP)�。圖1展示了不同特征尺寸(工藝技術(shù))的芯片(A10~A17)其晶體管數(shù)量隨年份的變化趨勢,從中能夠清晰看到摩爾定律的影響——通過不斷縮小芯片特征尺寸來增加晶體管數(shù)量��,從而拓展芯片的功能邊界。但遺憾的是��,隨著技術(shù)的不斷推進(jìn),依靠縮小特征尺寸(持續(xù)微縮)來制造SoC的難度越來越大����,同時(shí)成本也大幅攀升�����。相關(guān)調(diào)研數(shù)據(jù)顯示�����,圖2呈現(xiàn)了芯片設(shè)計(jì)成本隨特征尺寸縮小(直至5nm)的變化規(guī)律�����,僅完成5nm特征尺寸芯片的設(shè)計(jì)工作���,就需要超過5億美元的投入,而高良率5nm工藝技術(shù)的研發(fā)更是需要高達(dá)10億美元的資金支持����。此外��,圖3展示了芯片尺寸對(duì)研發(fā)制造良率的影響��,能夠發(fā)現(xiàn)�����,隨著芯片尺寸的增大,半導(dǎo)體制造的良率會(huì)呈現(xiàn)持續(xù)下降的態(tài)勢�����。

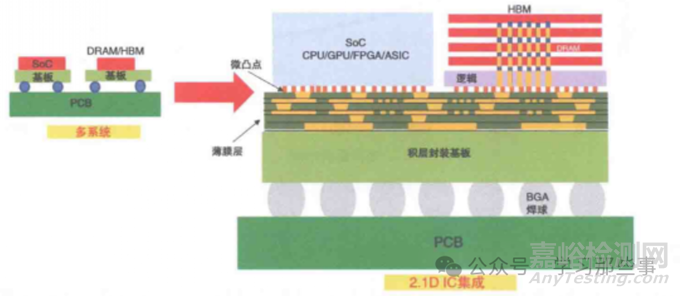

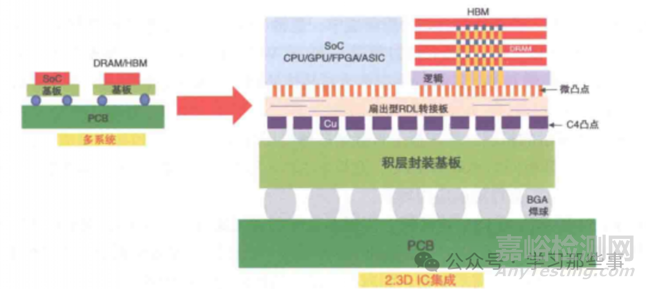

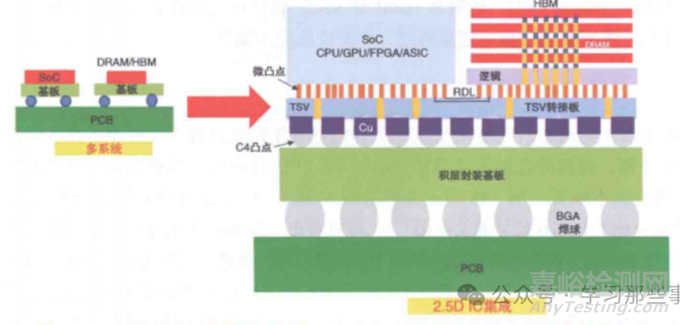

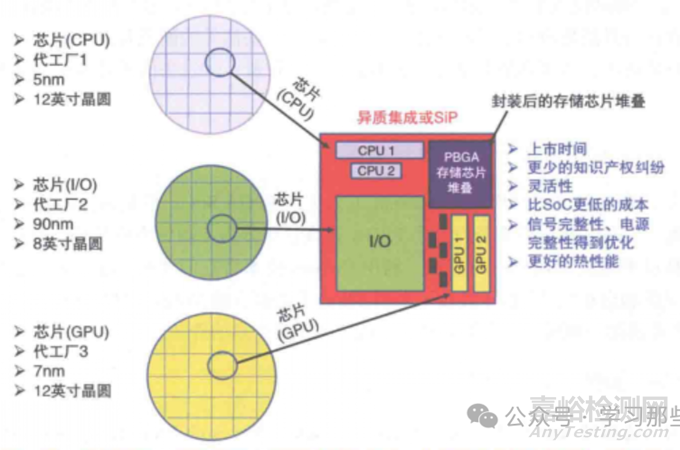

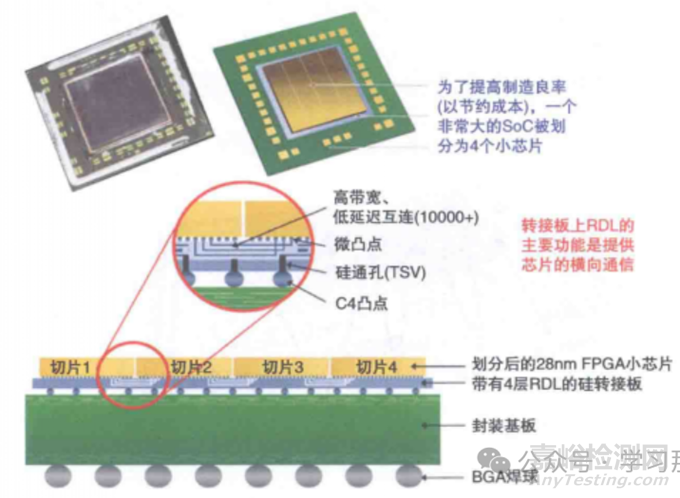

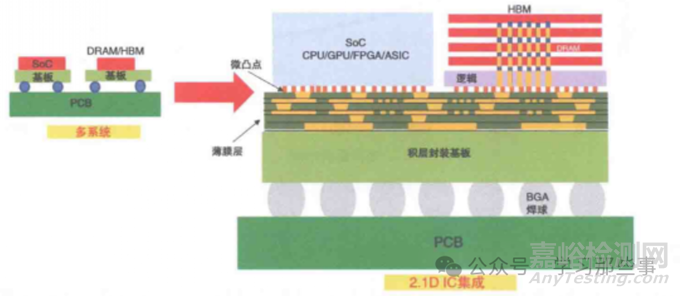

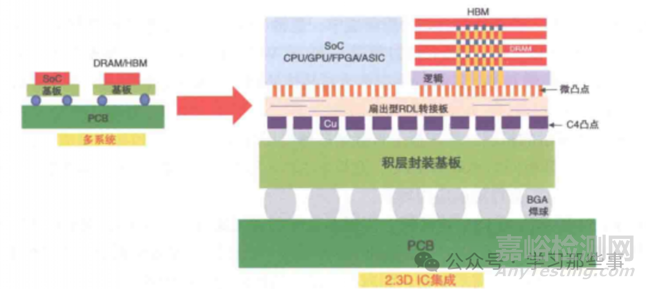

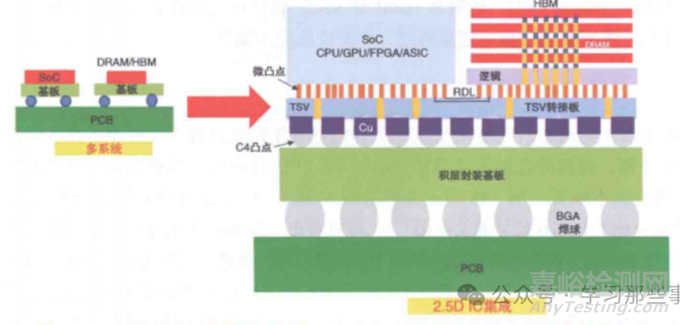

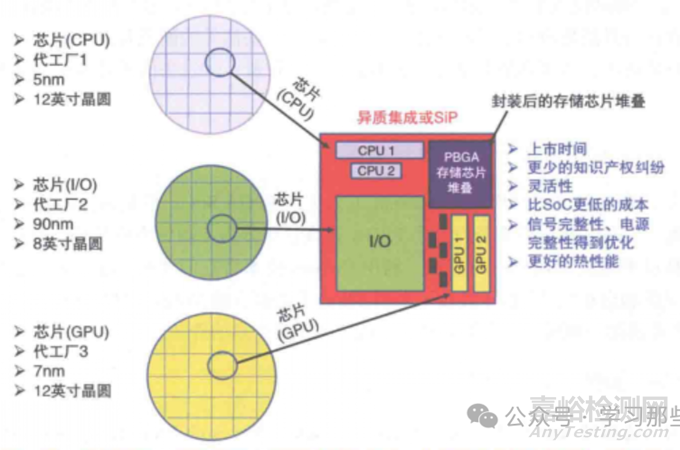

芯粒設(shè)計(jì)與異質(zhì)集成封裝是與SoC設(shè)計(jì)理念相對(duì)應(yīng)的一種新型技術(shù)路徑����。其核心思路是將傳統(tǒng)的SoC重新拆解設(shè)計(jì)為多個(gè)更小的芯粒��,隨后通過先進(jìn)的封裝技術(shù)�����,將不同材料制成��、具備不同功能���、由不同設(shè)計(jì)企業(yè)和代工廠生產(chǎn)����,且擁有不同晶圓尺寸�����、不同特征尺寸的芯粒����,集成組裝為一個(gè)完整的系統(tǒng)或子系統(tǒng)(見圖4~圖8)�����。其中����,每一顆芯粒都是一個(gè)由可復(fù)用IP(知識(shí)產(chǎn)權(quán))模塊組成的功能性集成電路(IC)單元�����。目前���,行業(yè)內(nèi)已形成至少5種不同的芯粒設(shè)計(jì)與異質(zhì)集成封裝方法��,具體如下:①芯片分區(qū)與異質(zhì)集成��,主要由成本優(yōu)化和技術(shù)優(yōu)化需求驅(qū)動(dòng),如圖4a所示�����;②芯片切分與異質(zhì)集成�,主要由成本控制和良率提升需求驅(qū)動(dòng)�����,如圖4b所示;③在積層封裝基板上直接制造薄膜層�����,進(jìn)而實(shí)現(xiàn)多系統(tǒng)和異質(zhì)集成(即2.1D IC集成),如圖5所示���;④在無TSV轉(zhuǎn)接板上實(shí)現(xiàn)多系統(tǒng)和異質(zhì)集成(即2.3D IC集成),如圖6所示����;⑤在TSV轉(zhuǎn)接板上實(shí)現(xiàn)多系統(tǒng)和異質(zhì)集成(即2.5D和3D IC集成)����,如圖7所示�。

在圖4a所示的芯片分區(qū)與異質(zhì)集成方案中����,包含邏輯單元和I/O接口的SoC芯片,會(huì)按照功能模塊劃分為邏輯芯粒和I/O芯粒���。這些芯粒可通過前道芯片-晶圓(CoW)鍵合或晶圓-晶圓(WoW)鍵合工藝完成堆疊集成���,之后再采用異質(zhì)集成技術(shù),將其組裝在單個(gè)封裝體的同一基板上���,具體如圖8所示。需要強(qiáng)調(diào)的是�,前道工藝芯粒集成能夠?qū)崿F(xiàn)更小的封裝面積和更優(yōu)的電氣性能,但這并非該方案的必需步驟�。

在圖4b所示的芯片切分與異質(zhì)集成方案中�,邏輯芯片等SoC會(huì)被切分為多個(gè)更小的芯粒��,例如邏輯1��、邏輯2和邏輯3��,隨后通過前道CoW或WoW工藝完成堆疊集成����,再利用異質(zhì)集成封裝技術(shù),將邏輯芯粒和I/O芯粒組裝在單個(gè)封裝體的同一基板上����。同樣���,芯粒的前道集成工藝并非該方案的必需環(huán)節(jié)��。

在圖5所示的積層封裝基板上直接制造薄膜層并實(shí)現(xiàn)多系統(tǒng)和異質(zhì)集成方案中,一塊帶有薄膜層的積層封裝基板會(huì)同時(shí)承載CPU�����、邏輯芯片和HBM等SoC組件�����。該技術(shù)主要由高性能��、小尺寸的應(yīng)用需求驅(qū)動(dòng),適用于高密度�����、高性能的應(yīng)用場景��。

在圖6所示的無TSV轉(zhuǎn)接板上實(shí)現(xiàn)多系統(tǒng)和異質(zhì)集成方案中,一塊精細(xì)金屬L/S RDL基板(有機(jī)轉(zhuǎn)接板)會(huì)同時(shí)承載CPU、邏輯芯片和HBM等SoC組件���,轉(zhuǎn)接板則安裝在積層封裝基板上�����。該技術(shù)同樣由高性能�����、小尺寸的應(yīng)用需求驅(qū)動(dòng)�����,面向高密度、高性能的應(yīng)用場景�����。

在圖7所示的TSV轉(zhuǎn)接板上實(shí)現(xiàn)多系統(tǒng)和異質(zhì)集成方案中�����,一塊無源(2.5D)或有源(3D)TSV轉(zhuǎn)接板會(huì)同時(shí)承載CPU�����、邏輯芯片和HBM等SoC組件,轉(zhuǎn)接板安裝在積層封裝基板上����。該技術(shù)由高性能、小尺寸的應(yīng)用需求驅(qū)動(dòng)��,主要面向超高密度�����、超高性能的應(yīng)用場景�����。

芯粒設(shè)計(jì)與異質(zhì)集成封裝的優(yōu)點(diǎn)和缺點(diǎn)2026

與傳統(tǒng)SoC相比�����,芯粒設(shè)計(jì)與異質(zhì)集成的核心優(yōu)勢體現(xiàn)在制造過程中良率的顯著提升��。無論是采用芯片分區(qū)還是芯片切分的方式,得到的芯粒尺寸都遠(yuǎn)小于傳統(tǒng)SoC�����,因此能夠有效提高半導(dǎo)體制造的良率���,進(jìn)而降低制造成本。圖3展示了單片設(shè)計(jì)與2顆�、3顆�����、4顆芯粒設(shè)計(jì)對(duì)應(yīng)的每片晶圓良率(良好芯片百分比)與芯片尺寸的關(guān)系���,數(shù)據(jù)顯示,360mm²的單片芯片良率僅為15%��,而4顆芯粒設(shè)計(jì)(單顆芯粒99mm²)的良率可提升一倍以上�����,達(dá)到37%��。雖然4顆芯粒設(shè)計(jì)會(huì)帶來約10%的面積損失(396mm²的總芯片面積中�����,用于各芯?���;ミB的硅面積為36mm²)��,但良率的大幅提升能夠直接轉(zhuǎn)化為制造成本的降低�����。與此同時(shí),芯片分區(qū)的設(shè)計(jì)方式還能有效縮短產(chǎn)品的上市周期�����,在CPU核的設(shè)計(jì)中�����,采用芯粒方法已被實(shí)踐證明可以有效降低設(shè)計(jì)和制造成本。此外�,由于芯粒分散布局在整個(gè)封裝體內(nèi)��,還能對(duì)芯片的熱性能起到一定的優(yōu)化作用���。

芯粒設(shè)計(jì)與異質(zhì)集成封裝也存在一定的劣勢�����,具體表現(xiàn)為:①接口設(shè)計(jì)需要額外的面積開銷���,可能導(dǎo)致封裝尺寸增大�;②封裝環(huán)節(jié)的成本相對(duì)更高����;③整體設(shè)計(jì)復(fù)雜度提升�,需要投入更多的設(shè)計(jì)工作量;④傳統(tǒng)的設(shè)計(jì)方法學(xué)難以完全適配芯粒設(shè)計(jì)的需求����。

賽靈思的芯粒設(shè)計(jì)與異質(zhì)集成封裝實(shí)踐2026

2011年,賽靈思委托臺(tái)積電采用28nm工藝生產(chǎn)FPGA SoC產(chǎn)品����,但由于芯片尺寸過大���,導(dǎo)致產(chǎn)品良率極低�。為此���,賽靈思對(duì)FPGA進(jìn)行了重新設(shè)計(jì)��,將其切分為4顆更小的芯粒��,具體如圖9所示。臺(tái)積電以高良率完成了這些切分后芯粒的制造��,并通過CoWoS技術(shù)將其集成在一起�����。2013年10月20日����,賽靈思與臺(tái)積電聯(lián)合發(fā)布了采用28nm工藝制造的Virtex-7HT系列芯片�,該產(chǎn)品成為業(yè)界第一款實(shí)現(xiàn)量產(chǎn)的芯粒設(shè)計(jì)與異質(zhì)集成封裝產(chǎn)品�����。

AMD的芯粒設(shè)計(jì)與異質(zhì)集成封裝實(shí)踐2026

在美國國防部高級(jí)研究計(jì)劃局(DARPA)通用異質(zhì)集成知識(shí)產(chǎn)權(quán)復(fù)用策略(CHIPS)項(xiàng)目的支持下�����,2017年UCSB與AMD聯(lián)合提出了一款面向未來的超高性能系統(tǒng)方案,如圖10所示�����。該系統(tǒng)包含一個(gè)中央處理器(CPU)芯粒����、多個(gè)圖形處理器(GPU)芯粒�����,以及位于無源轉(zhuǎn)接板和/或帶有RDL的有源TSV轉(zhuǎn)接板上的HBM存儲(chǔ)組件�����。

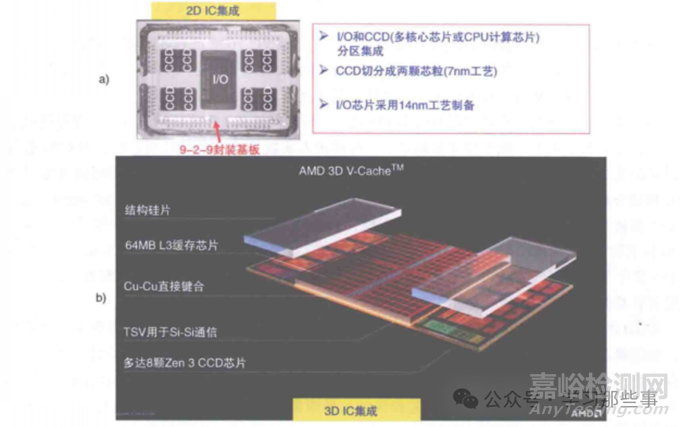

2019年年中��,AMD推出了代號(hào)為Rome的第二代EPYC 7002系列處理器����,該處理器的核心數(shù)量較上一代翻倍���,達(dá)到64個(gè)。這款Rome服務(wù)器產(chǎn)品采用9-2-9封裝基板實(shí)現(xiàn)信號(hào)連接��,在封裝基板芯板上設(shè)有4層布線�����,專門用于信號(hào)互連,具體如圖11a所示�����。高性能服務(wù)器和臺(tái)式機(jī)處理器通常具備大量的I/O接口�,而模擬器件和I/O接口的凸點(diǎn)節(jié)距在先進(jìn)技術(shù)節(jié)點(diǎn)上的優(yōu)化空間有限,且成本極高�����。針對(duì)這一問題,行業(yè)內(nèi)形成了兩種解決方案:一種是將SoC按功能分區(qū)為不同芯粒�����,為CPU核保留成本高昂的先進(jìn)工藝��,而I/O及存儲(chǔ)端口則采用上一代(n-1)工藝�����;另一種是將CPU核切分為更小的芯粒�����。在第二代EPYC芯片的設(shè)計(jì)中�����,每個(gè)多核心芯片或CPU計(jì)算芯片(CCD)都被切分為兩顆更小的芯粒����,AMD采用臺(tái)積電成本較高的7nm工藝(2019年初量產(chǎn))制造CCD核芯粒�����,而將DRAM和邏輯芯片轉(zhuǎn)移到格羅方德(GlobalFoundries)的成熟14nm工藝制造的I/O芯片上�。第二代EPYC芯片采用的是2D芯粒IC集成技術(shù),即所有芯粒均肩并肩放置在一塊9-2-9積層封裝基板上�,如圖11a所示。

AMD下一代芯粒設(shè)計(jì)與異質(zhì)集成封裝采用的是3D芯粒集成技術(shù)�����,即將芯粒堆疊在其他芯粒之上�,例如將功能芯粒堆疊在邏輯芯粒(也稱為有源TSV轉(zhuǎn)接板)上,如圖11b所示���。該圖展示的是采用3D V-Cache緩存堆疊技術(shù)的AMD Ryzen 9 5900X原型芯片�����,該技術(shù)能夠?qū)⒕彺嫒萘刻嵘猎兄笜?biāo)的3倍(從32MB提升至96MB L3 Cache)�����。第一款采用3D芯粒設(shè)計(jì)與異質(zhì)集成封裝的3D V-Cache芯片已于2022年第一季度正式出貨���。