概述2026

如圖1b所示��,在2.3DIC集成工藝中���,精細金屬線寬/線距(L/S)重分布層(RDL)基板(或有機轉接板)與積層封裝基板或高密度互連(HDI)板采用分開制造的方式���,兩者完成各自制備后,通過焊點實現(xiàn)互連�����,并采用底部填充料進行保護���,最終形成混合基板結構��。得益于臨時玻璃晶圓/面板的輔助制造工藝���,精細金屬L/S基板能夠實現(xiàn)2μm的線寬/線距規(guī)格,同時保持較高的生產良率�����。正是這種工藝優(yōu)勢��,使得2.3DIC集成的互連密度高于2.1DIC集成。

目前��,有機轉接板的制備方法至少有3種�����,具體分別為:①傳統(tǒng)半加成工藝(semi-additive process��,SAP)/印刷電路板(PCB)方法���;②先上晶扇出型方法���;③后上晶扇出型方法。表1對這3種制備方法進行了全面對比���,從對比結果中可得出以下結論:①由于需要額外進行晶圓凸點制備��、芯片與RDL基板鍵合以及底部填充等工序,SAP/PCB方法和后上晶扇出型方法的成本相對高于先上晶扇出型方法�����;②從承載能力來看��,SAP/PCB方法和后上晶扇出型方法能夠承載更大尺寸的芯片以及更大規(guī)格的封裝結構;③在精細度方面���,后上晶扇出型方法可實現(xiàn)RDL基板最小的金屬線寬/線距(L/S)���。

SAP/PCB方法2026

神鋼(Shinko)株式會社研發(fā)了無芯板有機轉接板,2012年該公司提出采用無芯板封裝基板替代硅通孔(TSV)轉接板���,具體結構如圖2所示���。可以明確的是�����,無芯板有機轉接板的制造成本遠低于TSV/RDL轉接板���,但該類型轉接板的翹曲控制一直是生產過程中的技術難題���。

思科(Cisco)公司也開發(fā)了專屬有機轉接板,圖3所示為該公司設計的基于大尺寸有機轉接板(無TSV結構)���,結合窄節(jié)距��、窄線寬互連工藝制造的芯粒及異質集成封裝結構���。該有機轉接板尺寸為38mm×30mm×0.4mm�����,共包含12層結構���,具體分層為5層頂部走線層、2層芯板層和5層底部走線層(5-2-5結構)���;與之搭配的封裝基板尺寸為50mm×50mm��,共包含4層結構�����,分別為1層頂部走線層�����、2層芯板層和1層底部走線層(1-2-1結構)。有機轉接板正面與背面的最小金屬線寬(L)���、線距(S)及金屬層厚度完全一致�����,分別為6μm�����、6μm和10μm���;轉接板(基板)共計10層走線層��,內部通孔尺寸為20μm��。在封裝布局上���,1顆尺寸為19.1mm×24mm×0.75mm的專用集成電路(application-specific integrated circuit,ASIC)芯片�����,與另外4顆由動態(tài)隨機存取存儲器(dynamic random-access memory�����,DRAM)堆疊形成的高帶寬存儲器(high bandwidth memory,HBM)共同搭載于有機轉接板上方�����。單顆3D HBM芯片尺寸為5.5mm×7.7mm×0.48mm��,由1顆底部緩沖芯片和4顆DRAM核芯片組成��,芯片之間通過硅通孔(through silicon via��,TSV)及帶有焊料帽的窄節(jié)距微凸點實現(xiàn)互連�����;有機轉接板正面焊盤尺寸為30μm���,焊盤節(jié)距為55μm�����。

先上晶扇出型方法2026

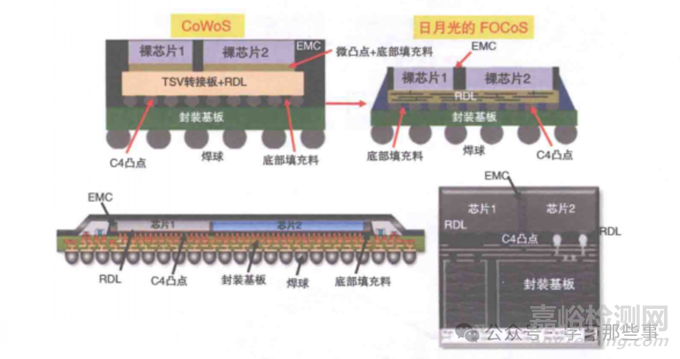

2013年���,星科金朋(Stats ChiPAC)提出采用先上晶扇出型倒裝芯片(fan-out chip-first flip-chip, FOFC)技術——即嵌入式晶圓級焊球陣列(embedded wafer level ball grid array, eWLB)技術,在芯片表面直接制作RDL,以此實現(xiàn)芯片大部分橫向與縱向通信功能���。根據相關專利(U.S.9484319B2,2011年12月23日提交)描述��,該技術的核心目的是采用RDL(無芯有機轉接板)替代傳統(tǒng)的TSV轉接板�����、微凸點及底部填充料�����,該專利于2016年11月1日正式獲得授權��。此后�����,聯(lián)發(fā)科(MediaTek)���、日月光(ASE)和臺積電(TSMC)等企業(yè)均開展了相關技術的研發(fā)工作��。圖4所示為日月光研發(fā)的扇出型板上芯片(fan-out chip-on-substrate�����,F(xiàn)OCoS)技術���,該技術先在臨時晶圓承載片上采用先上晶且面朝下的方式實現(xiàn)扇出�����,隨后通過模壓環(huán)氧模塑料(epoxy molding compound�����,EMC)完成包封工藝�����。

后上晶扇出型方法2026

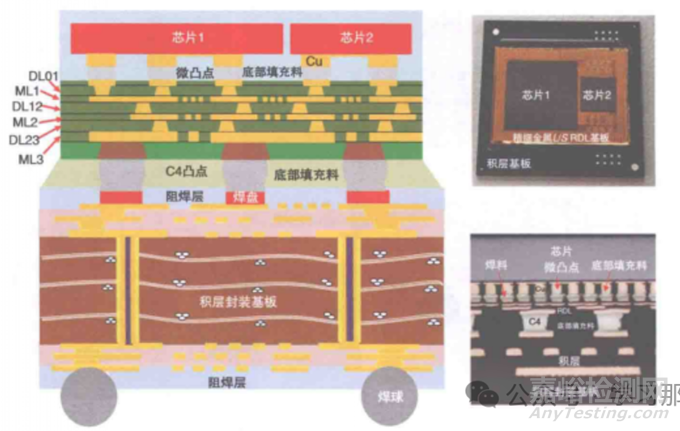

目前已有多家企業(yè)開展后上晶(或先上RDL)方法的研發(fā)���,旨在制備精細金屬L/S RDL基板(或有機轉接板),以替代TSV轉接板實現(xiàn)2.3DIC集成�����,其中包括矽品科技(SPIL)���、三星(Samsung)��、日月光(ASE)�����、臺積電(TSMC)��、神鋼(Shinko)及欣興電子(Unimicron)等�����。多數(shù)企業(yè)在制造RDL基板時�����,均會采用臨時晶圓作為支撐片�����。例如���,圖5和圖6分別為三星和日月光的2.3DIC集成結構,兩者的RDL基板均制備于臨時晶圓支撐片上�����;圖7和圖8為欣興電子的2.3DIC集成結構,其RDL基板則制備于臨時面板支撐片上���,該類型支撐片的產率高于臨時晶圓支撐片��。

精細金屬L/S基板與積層封裝基板或高密度互連(HDI)基板�����,同樣可與互連層進行搭配使用�����,這一應用方式與相關研究報道所述基本一致��,核心區(qū)別在于采用互連層替代了傳統(tǒng)的焊點和底部填充料���,具體結構如圖9所示。